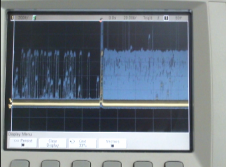

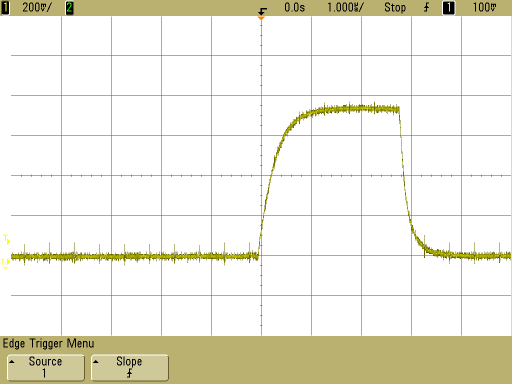

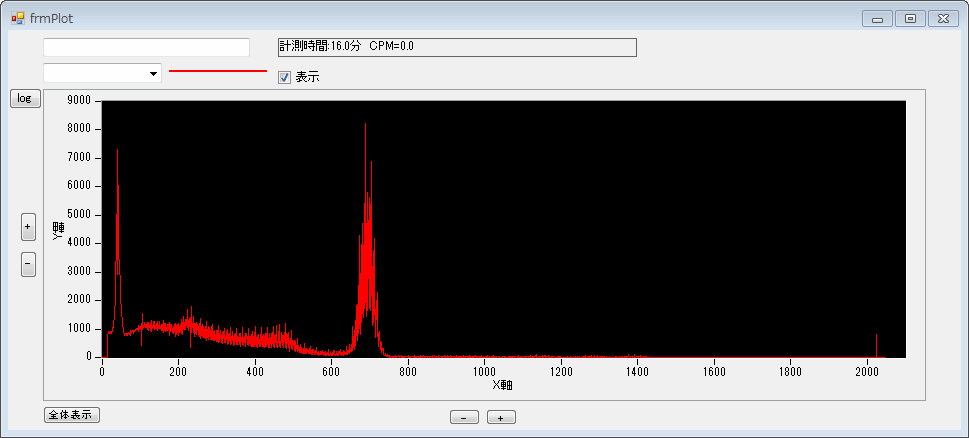

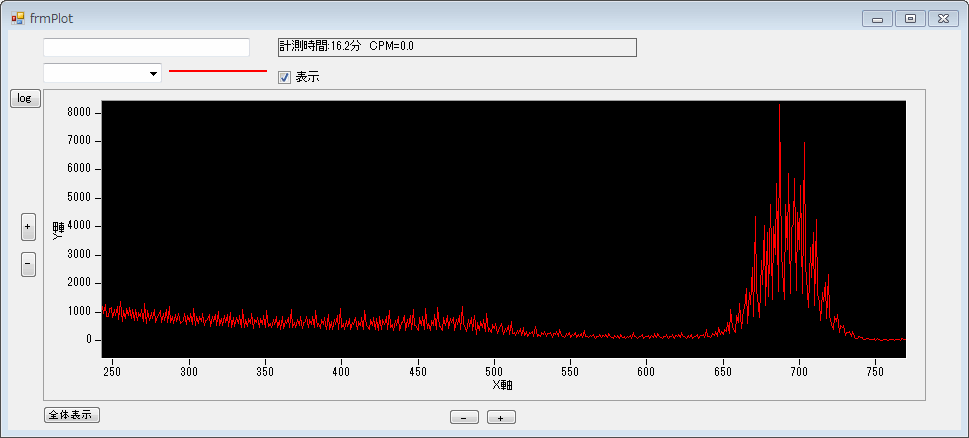

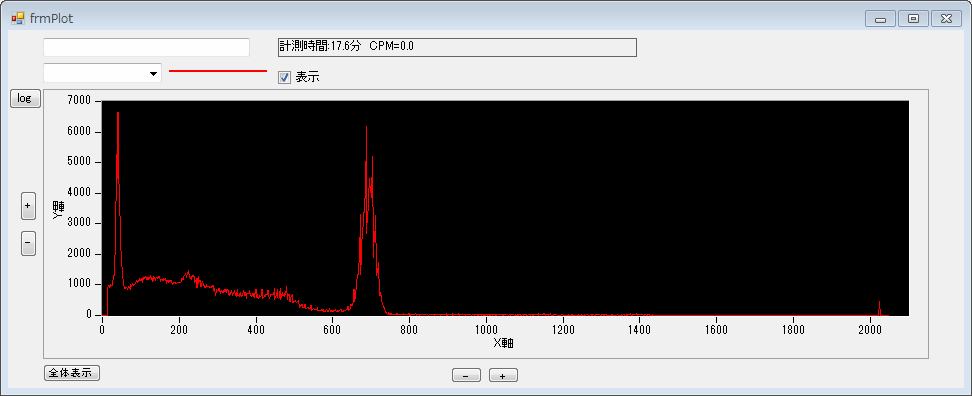

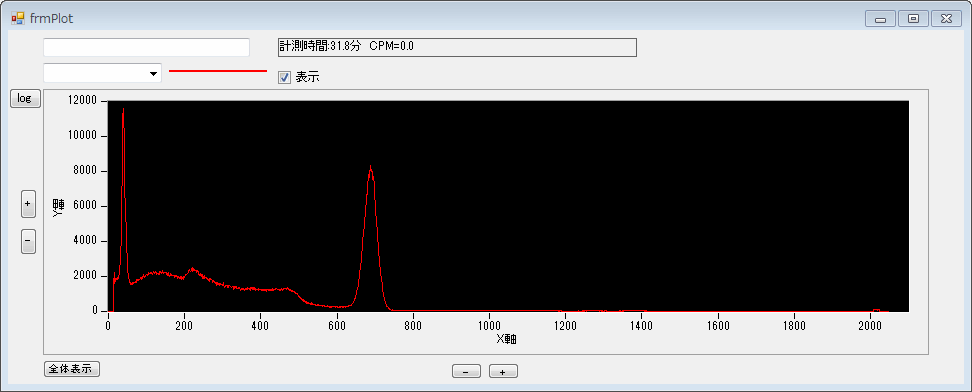

ガンマ線ディテクタからの出力パルスを観測すると興味深い事が分ります。次の動画を見ると観測する時間によりパルスの分布が違って見えます。この動画はCs137のガンマ線を観測したもので、中央のパルスでトリガーをかけ、その前後の時間のパルスを表示しています。時間軸(X軸)の単位は、1格子あたり、前半では20msec,後半では10μsecです。

この動画で、前半の画面の観測時間は200msecでこの程度の長い時間で見ると、パルス分布に偏りはなくアトランダムに一様に分布しています。それに対し、後半の画面は0.1msecと短い時間で観測したもので、分布は明らかに右側に偏っています。右側に偏るということは原子核の崩壊は1回起きると続いて崩壊する事が多い事を示しています。また、崩壊する前は時間が開く事が多い事も示しています。

放射性の原子核の崩壊は完全にアトランダムに起きます。このCs137の例では、ある崩壊と次の崩壊の間に因果関係もありません。しかし、オシロスコープで見るパルス分布は一つの崩壊が次の崩壊のきっかけになっているようにも見えます。一見矛盾するようにも思えますが、アトランダムに起きる事象はこのような分布をするという事が数学的にも証明されています。このような偏りはPoisson Clumping(ポアソンクランピング)と呼ばれています。